Sponsored by

www.ispsd2018.com

# 30th International Symposium on Power Semiconductor Devices and ICs

May 13-17, 2018, Chicago, USA

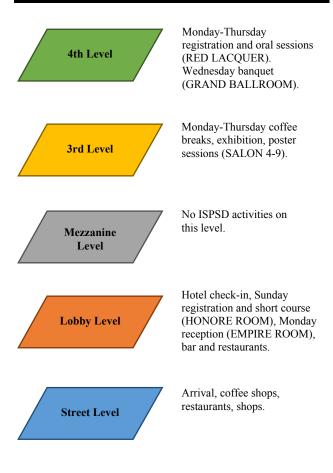

# PALMER HOUSE HILTON FLOOR DIRECTORY

You can use the elevator or escalator to get to any of these floors. There are numerous restaurant and bar options both inside and outside the hotel. Please use www.yelp.com to find your choices.

# SCHEDULE AT A GLANCE

| Sun. May 13                                                                                                                 | Mon. May 14                                                               |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Registration Desk<br>8:00-17:00<br>Honore Room (Lobby Level)                                                                | Registration Desk<br>7:00-17:00<br>Red Lacquer Room<br>(4th Level)        |

| Short Course 1: Silicon<br>Charge Balance Devices<br>9:00-10:00<br>Honore Room (Lobby Level)<br>Coffee Break<br>10:00-10:15 | Plenary 1<br>8:30-10:20<br>Red Lacquer Room<br>(4th Level)                |

| Short Course 2: Device<br>Loss Mechanisms<br>10:15-11:15                                                                    | Coffee Break<br>10:20-10:40<br>Salon 4-9 (3rd Level)                      |

| Coffee Break<br>11:15-11:30<br>Short Course 3: Sic Device                                                                   | Plenary 2<br>10:40-12:10<br>Red Lacquer Room<br>(4th Level)               |

| Design & Fabrication<br>1:30-12:30<br>Lunch on Own<br>12:30-14:00                                                           | Lunch on Own<br>12:10-14:00                                               |

| Short Course 4: Vertical<br>Gan Power Devices<br>14:00-15:00<br>Coffee Break                                                | 1. Superjunction MOS,<br>Diodes and IGBTs<br>14:00-15:40                  |

| 15:00-15:15<br>Short Course 5: Algan/Gan<br>Power Device Reliability                                                        | Red Lacquer Room<br>(4th Level)<br>Coffee Break                           |

| 15:15-16:15                                                                                                                 | 15:40-16:00                                                               |

| Coffee Break<br>16:15-16:30<br>Short Course 6: Power<br>Module Design and<br>Assembly<br>16:30-17:30                        | 2. SiC Power MOSFETs<br>16:00-18:05<br>Red Lacquer Room<br>(4th Level)    |

|                                                                                                                             | Reception<br>18:15-20:15<br>(badge required)<br>Empire Room (Lobby Level) |

# SCHEDULE AT A GLANCE

| Tue. May 15                                                                       | Wed. May 16                                                                                               | Thu. May 17                                                                         |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| 3. Lateral Devices:<br>Reliability                                                | 9. GaN Power<br>Devices – 2                                                                               | 15. Novel Device<br>Structures                                                      |

| 8:30-10:10                                                                        | 8:30-10:10                                                                                                | 8:30-10:10                                                                          |

| Red Lacquer Room<br>(4th Level)                                                   | Red Lacquer Room<br>(4th Level)                                                                           | Red Lacquer Room<br>(4th Level)                                                     |

| Coffee Break<br>10:10-10:30                                                       | Coffee Break<br>10:10-10:30                                                                               | Coffee Break<br>10:10-10:30                                                         |

| Salon 4-9 (3rd Level)                                                             | Salon 4-9 (3rd Level)                                                                                     | Salon 4-9 (3rd Level)                                                               |

| 4. Smart<br>Power ICs<br>10:30-12:10<br>Red Lacquer Room<br>(4th Level)           | Poster Sessions<br>10. Low Voltage<br>11. IC Design<br>12. SiC<br>10:30-12:10<br>Salon 4-9<br>(3rd Level) | <b>16. IGBTs</b><br>10:30-12:10<br>Red Lacquer Room<br>(4th Level)                  |

| Lunch on Own<br>12:10-13:30                                                       | Lunch on Own<br>12:10-13:30                                                                               | Lunch on Own<br>12:10-13:30                                                         |

| 5. GaN Power<br>Devices – 1<br>13:30-15:10<br>Red Lacquer Room<br>(4th Level)     | 13. SiC Reliability<br>and Ruggedness<br>13:30-15:10<br>Red Lacquer Room<br>(4th Level)                   | 17. Invited & Late<br>News Papers<br>13:30-15:10<br>Red Lacquer Room<br>(4th Level) |

| Coffee Break<br>15:10-15:30<br>Salon 4-9 (3rd Level)<br>Poster Sessions           | Coffee Break<br>15:10-15:30<br>Salon 4-9 (3rd Level)                                                      | Closing<br>15:10-15:40<br>Red Lacquer Room<br>(4th Level)                           |

| 6. High Voltage<br>7. GaN<br>8. Packaging<br>15:30-17:10<br>Salon 4-9 (3rd Level) | 14. Packaging<br>and Enabling<br>Technologies<br>15:30-17:35<br>Red Lacquer Room<br>(4th Level)           |                                                                                     |

| Ad Com<br>Meeting/Dinner<br>18:30-21:30<br>(invitation only)                      | Banquet<br>18:30-21:30<br>(card required)<br>Grand Ballroom<br>(4th Level)                                | <b>TPC Dinner</b><br>18:30-21:30<br>(invitation only)                               |

# **TABLE OF CONTENTS**

| Palmer House Hilton Floor Directory     | 1  |

|-----------------------------------------|----|

| Schedule at a Glance                    | 2  |

| General Chair's Message                 | 6  |

| Organization                            | 8  |

| Organizing Committee                    | 8  |

| Advisory Committee                      | 9  |

| Technical Program Committee             | 9  |

| General Information                     | 12 |

| ISPSD Hall of Fame                      | 16 |

| Awards                                  | 19 |

| The Ohmi Best Paper Award               | 19 |

| Charitat Award (Young Researcher Award) | 21 |

| Plenary Talks                           | 22 |

| Short Course                            | 23 |

| Technical Program                       | 29 |

| Partnership Organizations               | 52 |

| Gold Partners                           | 52 |

| Silver Partners                         | 52 |

| Exhibitors                              | 53 |

It is my great honor and pleasure to welcome you on behalf of the Organizing Committee to the 30th IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD 2018) in the beautiful city of Chicago.

ISPSD2018 marks the 30th anniversary of ISPSD. Since its first meeting in Japan in 1988, ISPSD has become the world's premier forum for technical discussions in all areas of power semiconductor devices and power integrated circuits. The global power semiconductor industry has steadily grown into a \$30 billion sector over the past three decades, enabling energy-efficient applications such as solar power, wind power, electric vehicles, ICT infrastructures, lighting and industrial drives. Over 1600 technical papers have been presented at ISPSD conferences. Most of the breakthrough power device technologies were first reported at ISPSD before they became phenomenal commercial successes. ISPSD2018 will celebrate 30 years of excellence in advancing power semiconductor technologies with a series of technical and social events during the conference. In particular, we will induct 32 distinguished colleagues into the newly established ISPSD Hall of Fame during the Wednesday 30th Anniversary Celebration Banquet. As a special celebration gift, we present you a complete collection of ISPSD proceedings 1988--2018 (including the two Electrochemical Society Workshops on High Voltage and Smart Power Devices and ICs in 1987 and 1989), thanks to the support of IEEE, IEEJ, ECS, and a group of dedicated volunteers.

Our plenary session on Monday will start with an opening keynote speech on "ISPSD: A 30 Year Journey in Advancing Power Semiconductor Technology" from three founding members of the conference, Drs. Ayman Shibib (USA), Leo Lorentz (Germany), and Hiromichi Ohashi (Japan), and followed by three other plenary speeches on "Silicon, GaN and SiC: There's Room for All" from Mr. Larry Spaziani, GaN Systems Inc., Canada, "Si Wafer Technology for Power Devices: A Review and Future Directions" from Mr. Norihisa Machida, SUMCO, Japan, and "The Future of Power Semiconductors: an EU Perspective" from Dr. Bert De Colvenaer, ECSEL, Belgium, respectively. We are extremely fortunate to have these distinguished leaders from industry to share their visions and wisdoms with us.

ISPSD2018 features 50 oral and 79 poster presentations on both silicon and WBG power devices which are selected from 245 abstracts from 23 countries/regions. On Sunday, we offer 6 short courses on a series of current and practical topics in the field.

Chicago is the third largest city in the United States, and an international hub for finance, commerce, industry, technology, telecommunications, and transportation. The city of Chicago is the birth place of modern skyscrapers and a living museum of modern architecture. ISPSD 2018 is held in the historical Palmer House Hilton Hotel in the beautiful and safe downtown district ("Loop") of Chicago with numerous museums, parks, theaters, restaurants, and shops within a walking distance. We trust you and your family will enjoy your stay in Chicago. On Monday, we will host our Welcome Reception in the splendid Empire Room of the Palmer House. On Wednesday, we expect to see you all at the 30th Anniversary Celebration Banquet to enjoy Chicago jazz/blues music, wines and delicious meals. Our family and companion programs offer exciting city tours on Monday, and Tuesday, and Wednesday.

We are pleased to acknowledge the support of our Gold Partners PowerAmerica and Sinopower Semiconductor, and Silver Partners Applied Materials, ShinDengen, Synopsys, and Tektronix. Their support and participation have created a very strong industrial relevance. We will have 17 exhibitors in the exhibition/coffee area (Salon 4-9 on the 3rd Floor) Monday through Thursday. The exhibitors will showcase their state-of-the-art technologies, products, and solutions, creating a highly interactive networking environment when mixing with the poster sessions and coffee breaks in the same space.

I would like to express my utmost gratitude to the members of the organizing committee, the technical program committee, and the advisory committee, who with hard work and selfless dedication have made this conference possible. I wanted to thank each and every one of you as a presenter, an attendee, an exhibitor, a volunteer, or any combined role of the above for your contribution and participation.

Once again I welcome you to ISPSD2018. Together we help deliver a more sustainable future.

Z. John Shen, General Chair

# **ORGANIZING COMMITTEE**

General Chair John Shen, Illinois Institute of Technology, USA

# Vice Chairs

Kuang Sheng, Zhejiang University, China Oliver Haeberlen, Infineon, Austria

**Technical Program Committee Chair** Wai Tung Ng, *University of Toronto, Canada*

Finance Chair Sujit Banerjee, Monolith Semiconductor, USA

Publicity Chair David Sheridan, AOS Semiconductor, USA

**Publication Chair** Olivier Trescases, *University of Toronto, Canada*

Short Course Chair Alex Huang, University of Texas at Austin, USA

Industrial Liaison and Expo Chair Victor Veliadis, *PowerAmerica*, USA

Local Arrangements Chair Anup Bhalla, USCi, USA

Webmaster Mengqi Wang, University of Toronto, Canada

# **ADVISORY COMMITTEE**

Gehan Amaratunga, Cambridge University, UK Tat-Sing Paul Chow, Rensselaer Polytechnic Institute, USA Mohamed Darwish. MaxPower Semiconductor, USA Don Disney, GlobalFoundries, USA Dan Kinzer, Navitas Semiconductor, USA Leo Lorenz, ECPE, Germany Gourab Majumdar, Mitsubishi Electric, Japan Peter Moens, ON Semiconductors, USA Mutsuhiro Mori, Hitachi, Ltd., Japan Hiromichi Ohashi, NPERC-J, Japan Yasukazu Seki, Fuji Electric Co., Ltd., Japan M. Ayman Shibib, Vishav Siliconix, USA Johnny Sin, Hong Kong Univ. of Science and Technology, China Jan Šonský, NXP Semiconductors, Belgium Yoshitaka Sugawara, Ibaraki University, Japan Richard K. Williams, Adventive Technology, USA Toshiaki Yachi, Tokyo University of Science, Japan

# **TECHNICAL PROGRAM COMMITTEE**

## Chair

Wai Tung Ng, University of Toronto, Canada

#### **Category 1: High Voltage Power Devices (HV)**

Category Chair Anup Bhalla, United Silicon Carbide, USA

## Members

Marina Antoniou, University of Cambridge, UK Giovanni Breglio, University of Naples Federico II, Italy Young Chul Choi, ON Semiconductor, Korea (in USA) Thomas Laska, Infineon Technologies, Germany Xiaorong Luo, UESTC, China Tadaharu Minato, Mitsubishi, Japan Yasuhiko Onishi, Fuji Electric, Japan Wataru Saito, Toshiba Corporation, Japan Jan Vobecky, ABB, Switzerland Chongman Yun, Trinno Technology, Korea Shuai Zhang, TSMC, China

## Category 2: Low Voltage Devices and Power IC Device Technology (LVT) Category Chair

Phil Rutter, Nexperia, UK

#### Members

Jun Cai, Texas Instruments, USA Naoto Fujishima, Fuji Electric, Japan Dev Alok Girdhar, Intersil, USA Alexander Hölke, XFAB, Malaysia Kenya Kobayashi, Toshiba Corporation, Japan Yoshinao Miura , Renesas Electronics, Japan Purakh Raj Verma, UMC, Taiwan Ronghua Zhu, NXP Semiconductors, USA

# Category 3: Power IC Design (ICD)

Category Chair Olivier Trescases, University of Toronto, Canada

#### Members

David Tsung-Yi Huang, *Richtek, Taiwan* Hoi Lee , *UT Dallas, USA* Takahiro Mori, *Renesas, Japan* Shuichi Nagai, *Panasonic, Japan* Nicolas Rouger, *CNRS, France* Junichi Sakano, *Hitachi, Japan* Weifeng Sun, *Southeast University, China* Maarten Swanenberg, *NXP Semiconductors, Holland* Budong (Albert) You, *Silergy Corp., China* Alessandro Zafarana, *STMicroelectronics, Italy*

# Category 4: GaN and Nitride Base Compound Materials (GaN)

Category Chair Tom Tsai, *TSMC, Taiwan*

#### Members

Kevin Chen, Hong Kong University of Science and Technology, China Oliver Haeberlen, Infineon Technologies, Austria Alex Huang, North Carolina State University, USA Yang Liu, Sun Yat-sen University, China Peter Moens, ON Semiconductor, Belgium Sameer Pendharkar, Texas Instruments, USA Jun Suda, Nagoya University, Japan Tom Tsai, TSMC, Taiwan Yasuhiro Uemoto, Panasonic, Japan

# Category 5: SiC and Other Materials (SiC)

Category Chair Peter Losee, *GE*, *USA*

#### Members

Philippe Godignon, CNM institute, Spain Chih-Fang Huang, National Tsing Hua University, Taiwan Takeharu Kuroiwa, Mitsubishi Electric, Japan Chwan Ying Lee, Hestia-Power Inc., Taiwan Kung-Yen Lee, National Taiwan University, Taiwan Kevin Matocha, Monolith Semiconductor, USA Andrei Petru Mihaila, ABB, Switzerland David Sheridan, Alpha & Omega Semiconductor, USA Ranbir Singh, GeneSiC, USA Jun Suda, Nagoya University, Japan Victor Veliadis, Power America, USA Yoshiyuki Yonezawa, AIST, Japan Jon Zhang, Wolfspeed, USA

# Category 6: Module and Package Technologies (PK)

**Category Chair** Alberto Castellazzi, *Nottingham University, UK*

#### Members

Sven Berberich, Semikron, Germany Josef Lutz, Technical University of Chemnitz, Germany Tomoyuki Miyoshi, Hitachi, Japan Hiroshi Tadano, University of Tsukuba, Japan

# **Conference Venue**

Palmer House Hilton 17 E Monroe St, Chicago, IL 60603 +1 (312) 726-7500

Conference discount room rates are available via <u>www.ispsd2018.com</u> until April 13, 2018. Please use the floor directory on Page 2 for detailed meeting room information.

# **Conference Registration**

In order to participate in the ISPSD2018 conference, you must register online for the conference at <u>www.ispsd2018.com</u> using your credit card. You need to wear your badge in all conference activities. The conference reception desk hour/location information is as the following:

| Sunday, May 13    | 8:00-17:00 | Honore Room, Lobby Level    |

|-------------------|------------|-----------------------------|

| Monday, May 14    | 7:00-17:00 | Red Lacquer Room, 4th Level |

| Tuesday, May 15   | 8:00-17:00 | Red Lacquer Room, 4th Level |

| Wednesday, May 16 | 8:00-17:00 | Red Lacquer Room, 4th Level |

| Thursday, May 17  | 8:00-13:00 | Red Lacquer Room, 4th Level |

# **Registration Fees**

Early fees apply to registration applications completed by April 15, 2018.

|                                  | Early Fee | Late Fee |

|----------------------------------|-----------|----------|

| IEEE/IEEJ Member                 | \$650     | \$800    |

| Non-Member                       | \$750     | \$900    |

| Student IEEE Member              | \$350     | \$450    |

| Student Non-Member               | \$450     | \$500    |

| Short Course IEEE/IEEJ Member    | \$400     | \$500    |

| Short Course Non-Member          | \$500     | \$600    |

| Short Course Student IEEE Member | \$200     | \$250    |

| Short Course Student Non-Member  | \$250     | \$300    |

# Cancellation and Refund Policy for Completed Registrations

Conference registration cancellation requests made via email. Requests made before April 30, 2018 will be processed with a fee of \$75, after April 30, 2018 will be processed with a fee of \$200. Request made after May 13, 2018 will not be processed.

Short course registration cancellation requests made via email. Requests made before May 12, 2018 will be processed with a fee of \$50. Requests made after May 12, 2018 will not be processed.

#### Local Transportation Chicago-O'Hare International Airport

Distance from hotel:29km (18 mi)Travel time:50 minCost:\$5

Directions: We recommend taking the subway Blue Line from O'Hare International Airport (ORD) to Monroe Station. Palmer House Hilton is 3 minute walk from Monroe Station. This is the cheapest and often quickest way to get to the hotel from ORD.

If coming from domestic or international flights arriving at Terminals 1, 2 or 3, follow the signs in the airport to "CTA Trains" or "Trains to City." The train station is less than 10 minute walk from baggage claim in each of these 3 terminals. If arriving at International Terminal 5, follow the signs to the Airport Transit System (ATS). Ride the train to Terminal 2, then follow signs to "CTA Trains" or "Trains to City." Once at the Terminal 2 train station, use the vending machine to purchase a single-ride or multi-day card (Ventra Card).

For more information on the subway service ("the L"), please visit http://www.transitchicago.com/airports/.

## **Chicago Midway Airport**

| Distance from hotel: | 19km (12 mi) |

|----------------------|--------------|

| Travel time:         | 30 min       |

| Cost:                | \$2.45       |

Directions: We recommend taking the subway Orange Line from Midway International Airport (MDW) to Adams/Wabash Station. Palmer House Hilton is 3 minute walk from Adams/Wabash station. This is the cheapest and often quickest way to get to the hotel from MDW.

At the airport, simply follow the sign "CTA Trains" or "Trains to City" from the MDW terminal and use the vending machine at the train station to purchase a single-ride or multi-day card (Ventra Card). For more information on the subway service ("the L"), please visit www.transitchicago.com/airports/.

Alternate Options: You can also use a taxi or Uber service. The cost from ORD to the hotel is around \$40-\$60 and the travel time is between 40 and 60 minutes. The cost from MDW to the hotel is around \$20-\$30 and the travel time is between 20 and 40 minutes. We do not recommend renting a car due to the very high parking cost and traffic congestion in the city.

## Instruction for Oral Presentation

Each oral presentation is allocated 25 minutes, including 5 minutes for Q&A. We must use the on-site laptop PC in the session room for oral presentations (OS: Windows7, PowerPoint 2007 / 2010 / 2013 /

2016, and pdf format files are acceptable). The screen format is 4:3 and projector resolution is XGA ( $1024 \times 768$  pixel). Organizer cannot guarantee the quality of Macintosh-based presentations, so check in advance their Windows compatibility. Please bring your data USB to the operation desk in the front row of the conference room at least 30 minutes before the beginning of your session. Please meet with your session chairs at least 20 minutes prior to the start of your presentation, and be seated at the "Next Speaker's seat" located in the front row. Please contact the registration desk in case you need assistance.

## **Instruction for Poster Presentation**

Your poster should be no larger than 4' x 4'  $(1.2m \times 1.2m)$  in size. Your poster should be displayed on the assigned board by paper ID using pushpins (available at the poster room). No other adhesive material is permitted on the boards. Please set up your poster one hour before the start of your poster session (see the program schedule). You are responsible for removing the poster after the session. You are expected to be in front of your poster throughout the session to answer questions.

## **Recording and Photography Policy**

IEEE policy prohibits video recording or photographing of presentations unless permission from the presenter is obtained in advance. Photographing of people or social events is permitted.

#### Monday Welcome Reception

18:15-20:15 Monday May 14 in the Empire Room on Lobby Level.

Please join us for wine, beer, and snacks, catch up with old friends and make a few new friends. Please use your conference badge to participate (no separate ticket is required).

## Wednesday 30th Celebration Banquet

18:30-21:00 Wednesday, May 16 in Grand Ballroom on 4th Level.

Please join us to celebrate the 30th anniversary of ISPSD in a Chicago themed banquet with jazz/blues performance. 32 distinguished colleagues will be inducted into the newly established ISPSD Hall of Fame. You will need to use the special invitation card to enter the banquet.

The main entrée will be a combo dish of beef and sea scallop. Alternative options (vegetarian only, beef only, scallop only) can be arranged ONLY if you check with the registration desk when you check-in. Please also inform us during check-in if you do NOT plan to attend the banquet. This will help us better plan the banquet seating.

# Coffee Breaks, Poster Sessions, and Exhibition

Monday through Thursday in Salon 4-9 on 3rd Level (one level below our main meeting room).

We use the Salon space to relax, network, and stop by the tabletop exhibition during coffee breaks and the poster sessions. You can use escalator or elevator to move between the main meeting room (Red Lacquer on 4th Level) and the Salon.

# **Spouse and Guest Program**

ISPSD2018 is glad to organize the following tours and activities (tentatively) for families and guests. Please encourage your guest to stop by the hospitality desk in the registration area to check out the final schedule and make reservation:

**Chicago Architecture Foundation River Cruise Tour**: Estimated cost: \$40 per person. Estimated tour time: 2 hours, tentatively scheduled for Monday

**Chicago Architecture Walking Tour:** Estimated cost: \$20 per person. Estimated tour time: 2 hours, tentatively scheduled for Tuesday

Art Institute Chicago: Estimated cost: \$25 per person. Estimated tour time: 2-5 hours, tentatively scheduled for Wednesday

In addition, the following links provide best ways to tour the city on your own:

- Citypass: www.citypass.com/chicago

- Hop-on-hop-off bus: www.bigbustours.com/en/chicago/chicago-bus-tours/

The purpose of the ISPSD Hall of Fame (IHF) is to honor individuals who have made high impact contributions in advancing power semiconductor technology and/or in sustaining the success of ISPSD. Starting this year, the IHF replaces the traditional "Contributory Awards" and "Pioneer Awards". The AdCom has selected the following 32 distinguished colleagues as the first inductees into the ISPSD Hall of Fame:

| Michael S. Adler   | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences                 |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| G.A.J. Amaratunga  | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences                 |

| B. Jayant Baliga   | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences                 |

| Xingbi Chen        | for contributions to superjunction power semiconductor devices                                                                              |

| Tat-Sing Paul Chow | for contributions to silicon and wide<br>bandgap power semiconductor devices,<br>and his leadership role in organizing<br>ISPSD conferences |

| Mohamed Darwish    | for contributions to the advancement of<br>power semiconductor technology, and his<br>leadership role in organizing ISPSD<br>conferences    |

| Taylor R. Efland   | for contributions to power IC technology,<br>and his leadership role in organizing<br>ISPSD conferences                                     |

| Wolfgang Fichtner  | for contributions to MOS gated thyristors<br>and TCAD modeling tools, and his leader-<br>ship role in organizing ISPSD conferences          |

| Min-Koo Han        | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences                 |

| Phil Hower         | for contributions to power device safe<br>operating area study and power IC<br>technology                                                   |

| A. A. Jaecklin     | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences                 |

| Daniel Kinzer    | for contributions to power MOSFET technology, and his leadership role in organizing ISPSD conferences                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Leo Lorenz       | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences                             |

| Gourab Majumdar  | for contributions to IGBT and intelligent<br>power module technology, and his leader-<br>ship role in organizing ISPSD conferences                      |

| Jose Millan      | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences                             |

| Peter Moens      | for contributions to integrated power<br>technology and GaN power device and<br>reliability, and his leadership role in<br>organizing ISPSD conferences |

| Akio Nakagawa    | for contributions to IGBT and power IC technology                                                                                                       |

| Hiromichi Ohashi | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences                             |

| Tadahiro Ohmi    | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences                             |

| Masahiro Okamura | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences                             |

| James Plummer    | for contributions to MOS-bipolar power<br>devices and power ICs, and for inspiring<br>and training a new generation of device<br>researchers            |

| C. A. T. Salama  | for contributions to power IC technology,<br>and his leadership role in organizing<br>ISPSD conferences                                                 |

| Yasukazu Seki    | for contributions to IGBT technology,<br>and his leadership role in organizing<br>ISPSD conferences                                                     |

| M. A. Shibib     | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences                             |

| Dieter Silber       | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences          |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Paolo Spirito       | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences          |

| Yoshitaka Sugawara  | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences          |

| Yoshiyuki Uchida    | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences          |

| Harry Vaes          | for contributions to RESURF technology                                                                                               |

| Carl F. Wheatley    | for contributions to IGBT and radiation-<br>hard power device technology                                                             |

| Richard K. Williams | for contributions to trench power MOS-<br>FET and power IC technology, and his<br>leadership role in organizing ISPSD<br>conferences |

| Toshiaki Yachi      | for contributions to modern power semi-<br>conductor technology, and his leadership<br>role in organizing ISPSD conferences          |

Deceased members in BOLD

# THE OHMI BEST PAPER AWARD

The Best Paper Award was renamed to "The Ohmi Best Paper Award" in honor of the late Prof. Ohmi's outstanding contributions to the ISPSD. The Ohmi Best Paper Award will be granted to the author(s) of a paper determined to be the best overall in the ISPSD2018.

# ISPSD2017 THE OHMI BEST PAPER AWARD A Novel Hybrid Power Module with Dual Side-Gate HiGT and SiC-SBD

**Abstract:** In this paper, a novel hybrid power module using a new combination of dual side-gate HiGTs (high-conductivity IGBT) and SiC-SBDs is proposed. This combination achieves drastic switching loss reductions at a turn-off loss of -43%, a turn-on loss of -71%, and a reverse recovery loss of -98% compared with a conventional combination of trench gate HiGTs and U-SFDs (ultra soft & fast recovery diode). As a result, the proposed DuSH module (dual side-gate HiGT hybrid module) has an extremely low inverter loss of -50%, similar to SiC-MOSFETs.

**Yujiro Takeuchi** received the B.S. and M.S. degrees in maritime science from Kobe University, Hyogo-ken, Japan in 2010 and 2012. He joined Hitachi, Ltd., Ibarakiken, Japan, in 2012, where he has been engaged in research on power semiconductor devices.

**Tomoyuki Miyoshi** received the B.S., M.S., and Ph.D. in Tohoku University, Miyagi, Japan, in 2005, 2007, and 2015. In 2007, he joined Hitachi, Ltd., Japan. He is currently engaged in research and development of power device technologies.

**Tomoyasu Furukawa** received the B.S. and M.S. degrees in Hiroshima University in 2000 and 2002. He joined Hitachi, Ltd, Japan, in 2002. He is currently engaged in research and development of power device technologies.

Masaki Shiraishi received the B.S. and M.S. degrees in Tokyo Institute of Technology in 1996 and 1998. He joined Hitachi, Ltd, Japan, in 1998. He has been engaged in research and development of power semiconductor devices.

**Mutsuhiro Mori** received the B.E., M.E. and Ph. D. degrees in science and engineering from Waseda University, Tokyo, Japan. Since 1979, he has been with the Hitachi Research Laboratory, Hitachi, Ltd. He has been engaged in the research and development of optimal energy saving control systems with IT and power semiconductor devices, such as the light-triggered thyris-

tors, GaAs power static induction transistors (SIT), one chip inverter ICs, high-voltage driver ICs, soft and fast recovery diodes (SFD), and high-conductivity insulated gate bipolar transistors (HiGT). He is a member of the Institute of Electrical Engineers of Japan (IEEJ) and a senior member of the Institute of Electrical and Electronics Engineers (IEEE).

# CHARITAT AWARD (YOUNG RESEARCHER AWARD)

A young researcher (age less than 30 at the time of the conference) who is both first author and presenter of a paper will be nominated to the award.

The Charitat award will be presented during the closing ceremony of the conference. The Ohmi best paper award will be presented during the ISPSD2019 opening session.

# ISPSD 2017 CHARITAT AWARD High Performance Fully-Recessed Enhancement-Mode GaN MIS-FET with Crystalline Oxide Interlayer

**Abstract:** In this work, we developed an effective technique to form a sharp and stable crystalline oxidation interlayer (COIL) between the reliable LPCVD (low pressure chemical vapor deposition)-SiN<sub>x</sub> gate dielectric and recess-etched GaN channel. The COIL was formed using oxygen-plasma treatment, followed by *in-situ* annealing prior to the LPCVD-SiN<sub>x</sub> deposition. The COIL plays the critical role of protecting the etched GaN surface from degradation during high-temperature (i.e. at ~ 780 °C) process, which is essential for fabricating enhancement-mode GaN MIS-FETs with highly reliable LPCVD-SiN<sub>x</sub> gate dielectric and fully recessed gate structure. The LPCVD-SiN<sub>x</sub>/GaN MIS-FETs with COIL deliver normally-off operation with a  $V_{TH}$  of 1.15 V, small on resistance, thermally stable  $V_{TH}$  and low positive-bias temperature instability (PBTI).

Mengyuan Hua received the B.S. degree in Physics from Tsinghua University, Beijing, China, in 2013. She then joined the Hong Kong University of Science and Technology (HKUST), Hong Kong, China, where she received the Ph.D. degree in Electronic and Computer Engineering in 2017 under the supervision of Prof. Kevin J. Chen. Currently, she is a research associate at

HKUST. Her research interests include GaN-based power device technology and device reliability.

#### PL1-1: ISPSD: A 30 Year Journey in Advancing Power Semiconductor Technology

Ayman Shibib, Vishay Siliconix, United States; Leo Lorenz, ECPE/ Infineon, Germany; Hiromichi Ohashi, NEPRC-J, Japan

**Abstract:** Celebrating the 30th Anniversary of ISPSD is a very special occasion to reflect on the origin and roots of the conference and how it came about to be the premier international conference on Power Semiconductor Devices and ICs. A review of the events that led to its formation and development is presented. Another aspect of this celebration is the review of the contributions of ISPSD to the Power Device technical community covering wide and diverse power device areas and applications throughout the 30 years history of ISPSD. The future prospects of Power Devices and ISPSD in the next years is briefly mentioned.

## PL1-2: Silicon, GaN and SiC: There's Room for All – An Application Space Overview of Device Considerations Larry Spaziani, Lucas Lu, *GaN Systems, Canada*

**Abstract:** The discrete power device marketplace is estimated between 15 and 22 billion dollars and is comprised primarily of transistors and diodes in a variety of voltage, current, packaging and power ratings. It is an area of intense focus as new technologies such as wide bandgap emerge and new applications such as electric vehicles emerge. Decision makers from Engineers to CEO's are faced with the same decisions they have always faced, comparing power, efficiency and size, yet the decisions are more difficult given the fast-moving pace of these emerging technologies. In this paper, several application spaces ranging from consumer to vehicle to motors will be reviewed, comparing the most critical aspects of the applications against semiconductor choices these decision makes have available. Considerations of the appropriate technologies will be reviewed comparing where the technologies have been, are to-day, and where they will be in the next 5 years.

# PL2-1: Si Wafer Technology for Power Devices: A Review and Future Directions

Norihisa Machida, SUMCO Corporation, Japan

**Abstract:** Silicon wafers have been widely used in semiconductor devices for years. Their characteristics have been improved by untiring development efforts to meet power device manufacturers' requirements such as lowering substrate resistivity for Power MOS-FET and reducing resistivity variation for IGBT. As future directions, by utilizing advantages of silicon wafers, adoption of MCZ grown bulk silicon wafers for low and middle voltage IGBT and introduction of 300mm size silicon wafers will proceed.

# PL2-2: The Future of Power Semiconductors: An EU Perspecitve

Bert De Colvenaer, ECSEL JU, Belgium

**Abstract:** With the integration of more renewable energy sources (RES) in the European landscape, with more stringent demands on supply and with cost conscious customers, and also environmental conscious, Europe calls for a smarter energy landscape where power semiconductors will play a major role in the years to come.

# SHORT COURSE

The short course this year is supported by Sinopower Semiconductor and other industrial partners.

| Time        | Title                          | Speaker            |

|-------------|--------------------------------|--------------------|

| 09:00-10:00 | Advances in Silicon Power      | Madhur Bobde       |

|             | Technology                     |                    |

| 10:00-10:15 | Coffee Break                   |                    |

| 10:15-11:15 | Perspective of Loss Mechanisms | Gerald Deboy       |

|             | in Silicon and Wide Bandgap    |                    |

|             | Power Devices                  |                    |

| 11:15-11:30 | Coffee Break                   |                    |

| 11:30-12:30 | Silicon Carbide Power Device   | Victor Veliadis    |

|             | Design and Fabrication: Making |                    |

|             | the Transition from Silicon    |                    |

| 12:30-14:00 | Lunch Break                    |                    |

| 14:00-15:00 | Vertical GaN Power Devices     | Isik C. Kizilyalli |

| 15:00-15:15 | Coffee Break                   |                    |

| 15:15-16:15 | AlGaN/GaN Power Device         | Peter Moens        |

|             | Reliability                    |                    |

| 16:15-16:30 | Coffee Break                   |                    |

| 16:30-17:30 | Multi-Chip Semiconductor       | A. Castellazzi     |

|             | Power Module Design and        |                    |

|             | Assembly: Rethinking           |                    |

|             | Established Packaging          |                    |

|             | Solutions for Improved         |                    |

|             | Performance, Robustness and    |                    |

|             | Reliability                    |                    |

# SC1. Advances in Silicon Power Technology

Madhur Bodge, Alpha & Omega Semiconductor

**Abstract:** Silicon power MOSFETs have made tremendous advancements in the past decade. The key concept that has led to this is that of charge balance. In conventional power MOSFET device the maximum doping level and the thickness of the drift region is limited by blocking voltage constraints and a triangular electric field results in its sub-optimal utilization.

The concept of charge balance involves adding an opposite polarity of charge in the drift region compared to default doping to modify the shape of electric field from triangular to trapezoidal for better utilization of drift region for voltage blocking and allow significantly higher doping concentration for lower conduction losses. For low voltages (below 400V) the popular device structure to achieve this is the Split Gate Transistor (SGT). This device utilizes trench MOS charge balance with a shield electrode under the gate. In addition to significantly improving the On Resistance per unit area ( $\sim$ 3x for 100V blocking), the shield electrode also significantly reduced the gate to drain miller capacitance (Crss) and Crss/Ciss ratio to allow for high frequency switching.

For high voltages above 400V, the depth of trench and thickness of liner oxide make SGT device impractical to fabricate. As a result, the Super-Junction transistor has emerged as the most successful MOSFET for high voltages. This device utilizes alternating P and N columns in the drift region thereby creating a charge balance. Methods such as multi epi, deep trench and fill have been demonstrated and are commercially successful for making superjunction transistors. These can achieve an On-Resistance reduction of up to 8x compared to planar DMOS transistor. However, presence of alternating P and N columns also results in peculiar Capacitance curves, particularly the Crss which drops sharply at low drain biases and then increases at higher drain biases. It also exhibits snappy diode reverse recovery.

Charge balanced structure is also finding use in bipolar devices such as IGBT and Fast recovery diodes. In these devices, charge balance is used for various performance enhancements such as improving turn-off losses, injection enhancement, and controlling injection efficiency for faster switching.

The goal of this seminar is to understand the device physics and electrical characteristics of charge balanced devices in unipolar and bipolar power devices. This seminar is intended for intermediate level audience.

# SC2. Perspective of Loss Mechanisms in Silicon and Wide Bandgap Power Devices

Dr. Gerald Deboy, Infineon Technologies Austria AG

**Abstract:** This short course will discuss switching losses for power semiconductor devices from a physical device point of view. The focus will be laid on power MOSFETs based on Superjunction technology and GaN high electron mobility transistors as two prominent examples of the silicon and the wide bandgap world. We will give a perspective of loss mechanisms in the light of recent developments of the two fundamental device concepts.

Based on these loss mechanisms appropriate circuits and control methods are discussed yielding best efficiency for both device concepts respectively.

The short course addresses researchers interested in a deep understanding of the device properties as well as users of modern power semiconductor devices seeking best matching between topology, control and power device.

# SC3. Silicon Carbide Power Device Design and Fabrication: Making the Transition from Silicon

Victor Veliadis, PhD, *Deputy Executive Director and CTO*, *PowerAmerica*

Abstract: The tutorial will outline the advantages of SiC over other power electronic materials, and will introduce SiC devices currently developed for power electronic applications. ESD, high-voltage testing, and packaging aspects will be covered. The design and properties of SiC JFETs, MOSFETs, BJTs, IGBTs, Thyristors, and Junction Barrier Schottky and PiN diodes will be discussed, with an emphasis on their performance advantages over those of their Si counterparts. Common SiC Edge Termination techniques, which allow SiC devices to exploit their full high-voltage potential, will be rigorously treated and their impact on device performance will be highlighted. Aspects of device fabrication will be taught with an emphasis on the processes that do not carry over from the mature Si manufacturing world and are thus tailored to SiC. In particular, the tutorial will stress in more detail the design and fabrication of SiC MOSFETs, which are being inserted in the majority of SiC based power electronic systems. Device reliability will be reported through exemplary hard switching results. Exemplary SiC-based power electronics systems like hybrid loaders, fast chargers, PV inverters, EV traction, and circuit breakers will highlight the significant advantages of these systems over their Silicon based counterparts.

This tutorial is intended for intermediate level audiences.

# SC4. Vertical Power Electronic Devices based on Bulk GaN Substrates

Dr. Isik C. Kizilyalli, Program Director at the Advanced Research Projects Agency – Energy (ARPA-E), Department of Energy

Silicon (Si) has been the semiconductor material of Abstract: choice for power devices for quite some time due to cost, ease of processing, and the vast amount of information available about its material properties. Si devices are, however, reaching their operational limits in blocking voltage capability, operation temperature, and switching frequency due to the intrinsic material properties of Si. Wide bandgap (WBG) power semiconductors, such as gallium nitride (GaN) and silicon carbide (SiC), are an attractive emerging alternative to Si in many applications. Power converters based on WBG devices can achieve both higher efficiency and higher gravimetric and volumetric power conversion densities than the equivalent Si based converters. The power figure of merit (PFOM), which captures the trade-off between the device specific resistance (Rsp) versus the device BV clearly illustrates the advantage of GaN over Si and SiC devices. This arises from the cubed dependence of the figure-of-merit on the critical electric field where the critical electric field for GaN is 10 times that of Si and 1.6 times that of SiC. To date, the majority of GaN power device development has been directed toward lateral architectures, such as high-electron mobility transistors (HEMTs), fabricated in thin layers of GaN grown on foreign substrates (including Si or SiC). Such lateral devices suffer from well-known issues such as current-collapse, dynamic onresistance, inability to support avalanche breakdown, and inefficient thermal management. Many of these shortcomings arise from defects originating in the very large lattice and coefficient of thermal expansion (CTE) mismatch between GaN and the substrate. Furthermore, most power electronics semiconductor and diodes are vertical architectures. Fabricating vertical semiconductor device structures on lattice and CTE matched bulk GaN substrates possible to realize the material-limited potential of GaN including true avalanche-limited breakdown and more efficient thermal management, leading to large device currents (> 100A) without resorting to device parallelization, high breakdown voltages (1.2 to 5kV), and increased number of die on a wafer. Recent availability of both 2and 4-inch bulk GaN substrates is enabling breakthroughs in GaN device performance with vertical diode structures. In this tutorial recent advances in bulk GaN substrates and vertical architecture GaN power electronic devices (diodes, transistors, and application circuits) is surveyed with emphasis on the ARPA-E (Department of Energy) funded projects in the SWITCHES and PNDIODES Programs along with recent significant advances made in Japan. The SWITCHES Program (launched 2013) aimed to catalyze the development of vertical GaN devices using innovations in materials and/or device architectures that drive the costs of the devices. The goal was to enable the development of high voltage (>1200V), high current (100A) single die power semiconductor devices that, upon

ultimately reaching scale, would have the potential to reach functional cost parity with Si power transistors while also offering breakthrough relative circuit performance (low losses, high switching frequencies, and high temperature operation). The PNDIODES (Power Nitride Doping Innovation Offers Devices Enabling SWITCHES, launched 2017) Program funds transformational advances and mechanistic understanding in the process of selective area doping in the III-Nitride wide band gap (WBG) semiconductor material system and the demonstration of arbitrarily placed, reliable, contactable, and generally useable p-n junction regions that addresses a major obstacle, enables high- performance and reliable GaN vertical power electronic semiconductor devices.

# SC5. AlGaN/GaN Power Device Reliability

Dr. Peter Moens, ON Semiconductor Belgium

**Abstract:** AlGaN/GaN power devices have made tremendous progress over the past few years, and first commercial products have entered the market. The quality of MOCVD has reached a level that allows the fabrication of large area transistors with high yield and good reproducibility. Although GaN power devices achieve substantial higher system efficiency compared to their Si counterparts, the widespread adoption of GaN power devices in the market is still hampered by the unknown field reliability.

The tutorial will focus on the current understanding of the different intrinsic and extrinsic reliability mechanisms of AlGaN GaN power devices, and will cover following aspects:

- A methodology on how to extract important information on the conduction mechanisms in the GaN buffer structure out of relatively simple measurements on TLM structures (backgating or substrate ramp) and transistors (current DLTS).

- Overview of the main intrinsic reliability mechanisms: gate reliability (both MISHEMT and pGaN gate), NBTI/PBTI of MISHEMTs, accelerated drain stress and hot carrier stress (semion-state stress). Recoverable versus permanent degradation.

- GaN-specific failure and degradation modes such as the inverse piezo-electric effect and dynamic Ron.

- Acceleration models and statistical distribution models (Weibull, lognormal) applied to GaN.

- Extrinsic reliability (HTRB, HTGB, thermal cycling etc).

- Switching reliability (double pulse testing, boost converter, ...)

- Introduction to the new upcoming JEDEC standard for Al-GaN/GaN power devices (JC 70.1).

The topic will be treated in-depth and is for an intermediateadvanced audience.

# SC6. Multi-Chip Semiconductor Power Module Design and Assembly: Rethinking Established Packaging Solutions for Improved Performance, Robustness and Reliability

Dr. Alberto Castellazzi, Associate Professor of Power Electronics, Power Electronics, Machines and Control Group University of Nottingham

Abstract: This short-course analyses the typical structure and assembly process of commercial power modules. Based on real application examples, it goes on to illustrate key operational electro- thermal and thermo-mechanical effects which prevent the achievement of disruptive efficiency, power density, robustness and reliability. It then presents innovative concepts and design approaches enabling progress beyond state-of-the-art and discusses the transfer of technology to new and upcoming wide-band-gap semiconductor technologies. In closing, package bespoke design methodologies and tools are addressed, with a focus on future virtual prototyping needs to support competitive development of increasingly integrated solutions.

The course targets an audience with entry to intermediate level knowledge of power device packaging; the topic is treated in general at the survey level, with some punctual aspects only dealt more in depth.

#### **Opening Remarks**

|       | Red Lacquer Room (4th Level)                     |  |  |

|-------|--------------------------------------------------|--|--|

| 08:30 | Monday, May 14, 2018                             |  |  |

|       | John Shen, Illinois Institute of Technology, USA |  |  |

#### 08:50 Plenary 1

Red Lacquer Room (4th Level) Monday, May 14, 2018 Chair: John Shen, Illinois Institute of Technology, USA Co-chair Kuang Sheng, Zhejiang University, China **ISPSD: 30 Year Journey in Advancing Power** 08:50 PL1-1 Semiconductor Technology Ayman Shibib, Vishay Siliconix, United States; Leo Lorenz, ECPE/Infineon, Germany; Hiromichi Ohashi, NEPRC-J, Japan 09:35 PL1-2 Silicon, GaN and SiC: There's Room for All -An Application Space Overview of Device Considerations Larry Spaziani, Lucas Lu, GaN Systems, Canada

#### 10:20 Coffee Break

Salon 4-9 (3rd Level) Monday, May 14, 2018

# Plenary 2

|       | Red Lacq | uer Room (4th Level)                        |

|-------|----------|---------------------------------------------|

|       | Monday,  | May 14, 2018                                |

|       | Chair:   | Wai Tung Ng, University of Toronto, Canada  |

|       | Co-chair | Kevin Chen, Hong Kong University of Science |

|       |          | and Technology, China                       |

| 10:40 | PL2-1    | Si Wafer Technology for Power Devices:      |

|       |          | A Review and Future Directions              |

|       |          | Norihisa Machida, SUMCO Corporation, Japan  |

| 11:25 | PL2-2    | The Future of Power Semiconductors:         |

|       |          | An EU Perspecitve                           |

|       |          | Bert De Colvenaer, ECSEL JU, Belgium        |

|       |          |                                             |

## 12:10 Lunch Break

Monday, May 14, 2018

|       | 1.                           | Superjunction MOS, Diodes and IGBTs            |  |

|-------|------------------------------|------------------------------------------------|--|

|       | Red Lacquer Room (4th Level) |                                                |  |

|       |                              | May 14, 2018                                   |  |

|       | Chair:                       | Young Chul Choi, ON Semiconductor, Korea       |  |

|       | Co-chair                     |                                                |  |

| 14:00 | 1-1                          | IGBT with Superior Long-Term Switching         |  |

|       |                              | Behavior by Asymmetric Trench Oxide            |  |

|       |                              | C. Sandow, P. Brandt, HP. Felsl,               |  |

|       |                              | FJ. Niedernostheide, F. Pfirsch, HJ. Schulze,  |  |

|       |                              | A. Stegner, F. Umbach, Infineon Technologies   |  |

|       |                              | AG, Germany; F. Santos, W. Wagner, Infineon    |  |

|       |                              | Technologies Austria AG, Austria               |  |

| 14:25 | 1-2                          | 6.5 kV Field Shielded Anode (FSA) Diode        |  |

|       |                              | Concept with 150C Maximum Operational          |  |

|       |                              | Temperature Capability                         |  |

|       |                              | B.K. Boksteen, C. Papadopoulos, D. Prindle,    |  |

|       |                              | A. Kopta, C. Corvasce, ABB Switzerland Ltd.,   |  |

|       |                              | Switzerland                                    |  |

| 14:50 | 1-3                          | Low Noise Superjunction MOSFET with            |  |

|       |                              | Integrated Snubber Structure                   |  |

|       |                              | Hiroaki Yamashita, Syotaro Ono, Hisao Ichijo,  |  |

|       |                              | Masataka Tsuji, Toshiba Electronic Devices &   |  |

|       |                              | Storage Corporation, Japan; Takenori Yasuzumi, |  |

|       |                              | Toshiba Corporation, Japan; Masaru Izumisawa,  |  |

|       |                              | Wataru Saito, Toshiba Electronic Devices &     |  |

|       |                              | Storage Corporation, Japan                     |  |

| 15:15 | 1-4                          | Breakthrough of Drain Current Capability       |  |

|       |                              | and On-Resistance Limits by Gate-Connected     |  |

|       |                              | Superjunction MOSFET                           |  |

|       |                              | Wataru Saito, Toshiba Electronic Devices &     |  |

|       |                              | Storage Corporation, Japan                     |  |

| 15.40 | Coffee B                     | reak                                           |  |

| 15.40 |                              | (3rd Level)                                    |  |

|       |                              | May 14, 2018                                   |  |

|       | wonday,                      | Way 14, 2010                                   |  |

## 2. SiC Power MOSFETs

# Monday, May 14, 2018

Red Lacquer Room (4th Level) Chair: Peter Losee, *General Electric, USA*

Co-chairAndrei Petru Mihaila, ABB, Switzerland16:002-1Investigation of Threshold Voltage Stability<br/>of SiC MOSFETs

Dethard Peters, Infineon Technologies AG, Germany, Thomas Aichinger, Infineon Technologies Austria AG, Austria, Thomas Basler, Infineon Technologies AG, Germany, Gerald Rescher, Infineon Technologies Austria AG, Austria, Katja Puschkarsky, Hans Reisinger, Infineon Technologies AG, Germany

| 16:25 | 2-2 | Deep-P Encapsulated 4H-SiC Trench<br>MOSFETs with Ultra Low R <sub>on</sub> Q <sub>gd</sub><br>Yasuhiro Ebihara, Aiko Ichimura, Shuhei Mitani,<br>Masato Noborio, Yuichi Takeuchi, Shoji Mizuno,<br>Toshimasa Yamamoto, Kazuhiro Tsuruta, <i>Denso</i><br><i>Corporation, Japan</i>                              |

|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16:50 | 2-3 | Influence of the Off-State Gate-Source Voltage<br>on the Transient Drain Current Response of<br>SiC MOSFETs<br>Christian Unger, Martin Pfost, <i>Technische</i><br>Universität Dortmund, Germany                                                                                                                 |

| 17:15 | 2-4 | Reduction of RonA Retaining High Threshold<br>Voltage in SiC DioMOS by Improved<br>Channel Design<br>Atsushi Ohoka, Masao Uchida, Tsutomu Kiyosawa,<br>Nobuyuki Horikawa, Kouichi Saitou,<br>Yoshihiko Kanzawa, Haruyuki Sorada,<br>Kazuyuki Sawada, Tetsuzo Ueda, <i>Panasonic</i><br><i>Corporation, Japan</i> |

| 17:40 | 2-5 | Avalanche Ruggedness and Reverse-Bias<br>Reliability of SiC MOSFET with Integrated<br>Junction Barrier Controlled Schottky Rectifier<br>Cheng-Tyng Yen, Fu-Jen Hsu, Chien-Chung Hung,<br>Chwan-Ying Lee, Lurng-Shehng Lee, Ya-Fang Li,<br>Kuo-Ting Chu, <i>Hestia Power Inc., Taiwan</i>                         |

# Reception

Empire Room (Lobby Level) Monday, May 14, 2018

18:15

#### Lateral Devices: Reliability 3.

|       | Red Lacquer Room (4th Level) |                                                 |  |

|-------|------------------------------|-------------------------------------------------|--|

|       | Tuesday, May 15, 2018        |                                                 |  |

|       | Chair:                       | Phil Rutter, Nexperia, UK                       |  |

|       | Co-chair                     | Jun Cai, Texas Instruments, USA                 |  |

| 08:30 | 3-1                          | Comprehensive Investigation on Mechanical       |  |

|       |                              | Strain Induced Performance Boosts in LDMOS      |  |

|       |                              | Wangran Wu, Siyang Liu, Jing Zhu,               |  |

|       |                              | Weifeng Sun, Southeast University, China        |  |

| 08:55 | 3-2                          | Investigation on Total-Ionizing-Dose            |  |

|       |                              | Radiation Response for High Voltage             |  |

|       |                              | Ultra-Thin Layer SOI LDMOS                      |  |

|       |                              | Xin Zhou, Lingfang Zhang, Ming Qiao,            |  |

|       |                              | Zhangyi'an Yuan, Ping Luo, University of        |  |

|       |                              | Electronic Science and Technology of China,     |  |

|       |                              | China; Lei Shu, Harbin Institute of Technology, |  |

|       |                              | China; Zhaoji Li, Bo Zhang, University of       |  |

|       |                              | Electronic Science and Technology of China,     |  |

|       |                              | China                                           |  |

|       |                              |                                                 |  |

| 09:20 | 3-3             | Electromigration Current Limit Relaxation<br>for Power Device Interconnects                           |

|-------|-----------------|-------------------------------------------------------------------------------------------------------|

|       |                 | Jungwoo Joh, Young-Joon Park, Srikanth Krishnan,<br>Kim Christensen, Jayhoon Chung,                   |

|       |                 | Texas Instruments, United States                                                                      |

| 09:45 | 3-4             | Performance and Reliability Insights of Drain                                                         |

|       |                 | Extended FinFET Devices for High Voltage                                                              |

|       |                 | SoC Applications                                                                                      |

|       |                 | B. Sampath Kumar, Milova Paul,                                                                        |

|       |                 | Mayank Shrivastava, Indian Institute of                                                               |

|       |                 | Science, India; Harald Gossner, Intel                                                                 |

|       |                 | Deutschland GmbH, Germany                                                                             |

| 10:10 | 10 Coffee Break |                                                                                                       |

|       |                 | (3rd Level)                                                                                           |

|       | Tuesday,        | May 15, 2018                                                                                          |

|       | 4.              | Smart Power ICs                                                                                       |

|       |                 | uer Room (4th Level)                                                                                  |

|       |                 | May 15, 2018                                                                                          |

|       | Chair:          | Nicolas Rouger, CNRS, France                                                                          |

|       | Co-chair        | Budong (Albert) You, Silergy Corp., China                                                             |

| 10:30 | 4-1             | High-Speed, High-Reliability GaN Power                                                                |

|       |                 | Device with Integrated Gate Driver                                                                    |

|       |                 | Gaofei Tang, Hong Kong University of Science                                                          |

|       |                 | and Technology, China; MH. Kwan, Taiwan                                                               |

|       |                 | Semiconductor Manufacturing Company Limited,                                                          |

|       |                 | Taiwan; Zhaofu Zhang, Jiabei He, Jiacheng Lei,                                                        |

|       |                 | Hong Kong University of Science and Technology,                                                       |

|       |                 | China; RY. Su, FW. Yao, YM. Lin, JL. Yu,                                                              |

|       |                 | Thomas Yang, Chan-Hong Chern, Tom Tsai,                                                               |

|       |                 | H.C. Tuan, Alexander Kalnitsky, Taiwan                                                                |

|       |                 | Semiconductor Manufacturing Company Limited,                                                          |

|       |                 | Taiwan; Kevin J. Chen, Hong Kong University of                                                        |

|       |                 | Science and Technology, China                                                                         |

| 10:55 | 4-2             | A 600V High-Side Gate Drive Circuit with                                                              |

|       |                 | Ultra-Low Propagation Delay for                                                                       |

|       |                 | Enhancement Mode GaN Devices                                                                          |

|       |                 | Yangyang Lu, Jing Zhu, Weifeng Sun, Southeast                                                         |

|       |                 | University, China; Yunwu Zhang, Southeast                                                             |

|       |                 | University and China Resources Microelectronics                                                       |

|       |                 | Limited, China; Kongsheng Hu, Zhicheng Yu,                                                            |

|       |                 | Jing Leng, Southeast University, China;                                                               |

|       |                 | Shikang Cheng, Sen Zhang, CSMC Technologies                                                           |

| 11.20 | 4.2             | Corporation, China                                                                                    |

| 11:20 | 4-3             | A Smart Gate Driver IC for GaN Power                                                                  |

|       |                 | Transistors<br>Lingday Vy, Wai Lie Zhang, Androw Shorton                                              |

|       |                 | Jingshu Yu, Wei Jia Zhang, Andrew Shorten,<br>Rophina Li, Wai Tung Ng, <i>University of Toronto</i> , |

|       |                 | Canada                                                                                                |

|       |                 | Cunuuu                                                                                                |

#### 11:45 4-4 [Late News] CMOS Bi-Directional Ultra-Wideband Galvanically Isolated Die-to-Die Communication Utilizing a Double-Isolated Transformer

Mahdi Javid, Arizona State University, United States; Karel Ptacek, ON Semiconductor, Czech Republic; Richard Burton, Atomera Inc., United States; Jennifer Kitchen, Arizona State University, United States

## 12:10 Lunch Break Tuesday, May 15, 2018

## 5. GaN Power Devices - 1

|       | Red Lacquer Room (4th Level) |                                                   |  |

|-------|------------------------------|---------------------------------------------------|--|

|       | Tuesday, May 15, 2018        |                                                   |  |

|       | Chair:                       | Kevin Chen, Hong Kong University of Science       |  |

|       |                              | and Technology, China                             |  |

|       | Co-chair                     | Oliver Haeberlen, Infineon Technologies, Austria  |  |

| 13:30 | 5-1                          | <b>Dynamic-Ron Control via Proton Irradiation</b> |  |

|       |                              | in AlGaN/GaN Transistors                          |  |

|       |                              | A. Tajalli, Università degli Studi di Padova,     |  |

|       |                              | Italy; A. Stockman, ON Semiconductor, CMST        |  |

|       |                              | imec/Ghent University, Belgium; M. Meneghini,     |  |

|       |                              | Università degli Studi di Padova, Italy;          |  |

|       |                              | S. Mouhoubi, A. Banerjee, ON Semiconductor,       |  |

|       |                              | Belgium; S. Gerardin, M. Bagatin, A. Paccagnella, |  |

|       |                              | E. Zanoni, Università degli Studi di Padova,      |  |

|       |                              | Italy; M. Tack, ON Semiconductor, Belgium;        |  |

|       |                              | B. Bakeroot, CMST imec/Ghent University,          |  |

|       |                              | Belgium; P. Moens, ON Semiconductor,              |  |

|       |                              | Belgium; G. Meneghesso, Università degli Studi    |  |

|       |                              | di Padova, Italy                                  |  |

| 13:55 | 5-2                          | <b>Bidirectional Threshold Voltage Shift and</b>  |  |

|       |                              | Gate Leakage in 650 V p-GaN AlGaN/GaN             |  |

|       |                              | HEMTs: The Role of Electron-Trapping and          |  |

|       |                              | Hole-Injection                                    |  |

|       |                              | Yuanyuan Shi, Qi Zhou, Qian Cheng, P. Wei,        |  |

|       |                              | L. Zhu, D. Wei, A. Zhang, Wanjun Chen,            |  |

|       |                              | Bo Zhang, University of Electronic Science and    |  |

|       |                              | Technology of China, China                        |  |

| 14:20 | 5-3                          | GaN-on-Si Lateral Power Devices with              |  |

|       |                              | Symmetric Vertical Leakage: The Impact of         |  |

|       |                              | Floating Substrate                                |  |

|       |                              | Hanyuan Zhang, Shu Yang, Kuang Sheng,             |  |

|       |                              | Zhejiang University, China                        |  |

## 14:45 5-4 Short Circuit Robustness Analysis of New Generation Enhancement-Mode p-GaN Power HEMTs

M. Riccio, G. Romano, L. Maresca, G. Breglio, A. Irace, *Università degli Studi di Napoli Federico II, Italy;* G. Longobardi, *University of Cambridge, United Kingdom*

# 15:10 Coffee Break

Salon 4-9 (3rd Level) Tuesday, May 15, 2018

# 15:30 Poster Session 6: High Voltage

Salon 4-9 (3rd Level), Supported by Sinopower Semiconductor.

#### Tuesday, May 15, 2018

Chair: Tadaharu Minato, Mitsubishi, Japan

Co-chair Tom Tsai, TSMC, Taiwan

- 6-1 Influence of Doping Profiles and Chip Temperature on Short-Circuit Oscillations of IGBTs Vera van Treek, Hans-Joachim Schulze, Franz-Josef Niedernostheide, Christian Sandow, Roman Baburske, Frank Pfirsch, Infineon Technologies AG, Germany

- 6-2 A 750V Recessed-Emitter-Trench IGBT with Recessed-Dummy-Trench Structure Featuring Low Switching Losses

Yao Yao, Haihui Luo, Qiang Xiao, Zhuzhou CRRC Times Electric Co., Ltd., China; Chunlin Zhu, Dynex Semiconductor Ltd., United Kingdom; Haibo Xiao, Rongzhen Qin, Zhuzhou CRRC Times Electric Co., Ltd., China; Luther-King Ngwendson, Dynex Semiconductor Ltd., United Kingdom; Xubin Ning, Canjian Tan, Zhuzhou CRRC Times Electric Co., Ltd., China; Ian Deviny, Dynex Semiconductor Ltd., United Kingdom; Xiaoping Dai, Zhuzhou CRRC Times Electric Co., Ltd., China

6-3 Small Current Unclamped Inductive Switching (UIS) to Detect Fabrication Defect for Mass-Production Phase IGBT Kazuya Sano, Yukio Matsushita, Megumi Yachi, Yoji Nakata, *Mitsubishi Electric Corporation, Japan;* Keiichiro Ide, Daisaku Yoshida, *Kyokuyo Semiconductors Corporation, Japan;* Tomohito Kudo, Yasuo Ata, Hideki Haruguchi, Shinya Soneda, Tadaharu Minato, *Mitsubishi Electric Corporation, Japan*

| 6-4  | Tother the Destance of Cities Destance                                                              |

|------|-----------------------------------------------------------------------------------------------------|

| 0-4  | Tailoring the Performance of Silicon Power<br>Diodes by Predictive TCAD Simulation of               |

|      | Platinum                                                                                            |

|      | Moritz Hauf, Christian Sandow, Franz-                                                               |

|      | Josef Niedernostheide, Infineon Technologies                                                        |

|      | AG, Germany; Gerhard Schmidt, Infineon                                                              |

|      | Technologies Austria AG, Austria                                                                    |

| 6-5  | Novel 3D Narrow Mesa IGBT                                                                           |

|      | Suppressing CIBL                                                                                    |

|      | Masahiro Tanaka, Nihon Synopsys G.K., Japan;                                                        |

|      | Akio Nakagawa, Nakagawa Consulting Office,                                                          |

|      | LLC., Japan                                                                                         |

| 6-6  | N-Buffer Design Optimization for Short Circuit                                                      |

|      | SOA Ruggedness in 1200V Class IGBT                                                                  |

|      | Kenji Suzuki, Koichi Nishi, Mitsuru Kaneda,                                                         |

|      | Akihiko Furukawa, Mitsubishi Electric                                                               |

|      | Corporation, Japan                                                                                  |

| 6-7  | High Avalanche Capability Specific Diode Part                                                       |

|      | Structure of RC-IGBT based upon CSTBT <sup>™</sup><br>Shinya Soneda, Shinya Akao, Tetsuo Takahashi, |

|      | Akihiko Furukawa, <i>Mitsubishi Electric</i>                                                        |

|      | Corporation, Japan                                                                                  |

| 6-8  | Coss Losses in Silicon Superjunction MOSFETs                                                        |

| 00   | across Constructions and Generations                                                                |

|      | Grayson Zulauf, Juan M. Rivas-Davila, Stanford                                                      |

|      | University, United States                                                                           |

| 6-9  | Extending the RET-IGBT (Recessed Emitter                                                            |

|      | Trench IGBT) Concept to High Voltages:                                                              |

|      | Experimental Demonstration of 3.3kV                                                                 |

|      | RET IGBT                                                                                            |

|      | L. Ngwendson, I. Deviny, C. Zhu, I. Saddiqui,                                                       |

|      | C. Kong, A. Islam, J. Hutchings, J. Thompson,                                                       |

|      | M. Briggs, O. Basset, Dynex Semiconductor Ltd.,                                                     |

|      | United Kingdom; H. Luo, Y. Wang, Y. Yao,<br>Zhuzhou CRRC Times Electric Co., Ltd., China            |